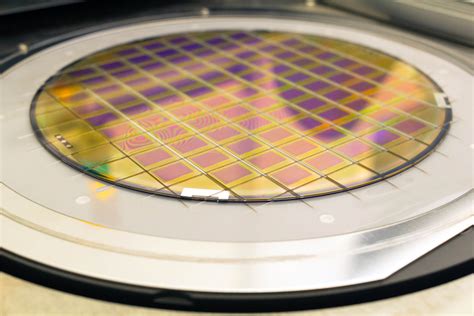

how is metal layer used in chip fabrication The microscope image below shows the lattice formed by seven metal layers. Each layer is flat and as they go higher, the layers get bigger to help reduce resistance. For Twisted Metal 2 on the PlayStation, a box shot for the US - 1996-10-31 release on GameFAQs.

0 · wafer to chip manufacturing process

1 · semiconductor wafer to chip

2 · semiconductor chip metallization material

3 · semiconductor chip manufacturing

4 · semiconductor chip fabrication process

5 · metal layers in semiconductor chips

6 · metal layers in semiconductor

7 · how to make semiconductor chips

“Excavation and Backfill for Structures.” Immediate backfilling is permitted for all junction box, manhole, and inlet structures where joints consist of rubber boots, rubbe. gaskets, or bulk or .

In modern semiconductor chips, the implementation of complex circuits requires multiple metallization layers. While the Front-End-of-Line (FEOL) layer designations vary between manufacturers and processes, the Back-End .In semiconductor device fabrication, the various processing steps fall into four general categories: deposition, removal, patterning, and modification of electrical properties. • Deposition is any process that grows, coats, or otherwise transfers a material onto the wafer. Available technologies include physical vapor deposition (PVD), This complex process involves the use of materials like silicon, epitaxial layers, photoresist, and metal and dielectric films to create microchips and other semiconductor devices. In this article, we will explore the purpose of . The microscope image below shows the lattice formed by seven metal layers. Each layer is flat and as they go higher, the layers get bigger to help reduce resistance.

Semiconductor chip layer development involves multiple steps, including deposition, photoresist, lithography, etching, ion implantation, and packaging. These steps require specialized equipment, facilities, and skilled .

To make a barrier metal, materials such as titanium (Ti) or cobalt (Co) are applied on top of the silicon layer of a semiconductor device, and the metal reacts with the silicon atoms. This process is called ‘silicidation’ while . To make any chip, numerous processes play a role. Let’s discuss six critical semiconductor manufacturing steps: deposition, photoresist, lithography, etch, ionization and packaging. Illustration by Aad Goudappel. .

Fabrication of chips on a wafer consists of hundreds of precisely controlled steps which result in a series of patterned layers of various materials one on top of another. What follows is a sample . Laying down metal highways that bring semiconductors to life . Utilizing metal’s conductive properties, the metal interconnect process creates metal circuits along the pre-designed patterns. The metal used for . The next step is EDS. This is the process of testing to ensure flawless semiconductor chips. In other words, it is a testing step to sort out defective chips. Yield is a percentage of prime chips relative to the maximum . Sputtering is commonly used to deposit the metal layer. In a vacuum chamber, a pure metal disk is positioned beneath an Ar (argon) ion cannon. Additionally positioned inside the chamber above the target are the .

wafer to chip manufacturing process

Usually either a metal, to act as a conductor, or putting down an oxide layer to act as an insulator. For that oxide layer, it's really just like putting the wafer in a furnace so it can heat up an oxidize. For deposting a metal, it get vaporized and mixed in with an inert gas before getting blasted at . 2. Lithography (i.e., printing): There are a few lithography methods, but the one used for high-volume chip fabrication is projection optical lithography.The semiconductor wafer is coated with aphotosensitive polymer film called a photoresist.Meanwhile, the design layout pattern is transferred to an opaque material called a mask.The optical lithography system projects the . Top Metal layer can be of either Mz or Mr (for metal stack more then 6). (Restriction provided by foundry) My, Mx Layer can't be Top metal layer. These are always inter-layer metal. (Restriction provided by foundry) M1 is always First metal layer. (Restriction provided by foundry) Sequence of Metal layer is M1 -> Mx -> My -> Mz/Mr.

This set of VLSI Multiple Choice Questions & Answers (MCQs) focuses on “nMOS and CMOS Fabrication”. 1. What is Lithography? a) Process used to transfer a pattern to a layer on the chip b) Process used to develop an oxidation layer on the chip c) Process used to develop a metal layer on the chip d) Process used to produce the chip View Answer The IC Layout Engineer is responsible for converting an electrical design to a mask layout used for chip fabrication. He is responsible for the physical representation of the chip, from the lowest . The dominance of soft lithography. Over the last decade, PDMS has become virtually the default material for forming microfluidic devices, 8 because of the sheer ease with which it can be cast on to a micro-scale mould and then strongly bonded to glass. 9 The elastomeric nature of the material has been exploited to integrate fluidic valves and pumps on . One of the biggest marketing terms associated with chip fabrication is the feature size. . The microscope image below shows the lattice formed by seven metal layers. Each layer is flat and as .

Furthermore, even when a metal or a material that is not heat-resistant like aluminum is used, contacts need to be formed with tungsten while aluminum wires are placed on top. Barrier Metals: Reducing Metal-to-Metal Resistance. Meanwhile, a metal—or metal compound—called a barrier metal is needed between the device and the contact.

The lot level lithography used in this process was RIT’s standard one-micron resist recipe. The GCA1006 coat track was used to coat one micron of positive photoresist. All parameters were set the same as RIT’s process. The GCA g-line stepper was used for exposure. A different stepper job was used to compensate for a slightly larger chip size.

As the LED chips are still closely arranged after dicing, the spacing is small (about 0.1mm), which is not conducive to the operation of the subsequent process. Use a chip expander to expand the film bonding the chips, make the LED chips draw to 0.6mm. Adopt Manual expansion, but it is easy to cause bad problems such as chip falling and waste. 3. Metal layers connect the points of the two ends. There can be many numbers of metal layers which has been used to complete the routing. The number of metal layers to be used depend upon the foundry and technology node. Normally for 7nm TSMC technology node, 14 Metal layers are used and in 7nm Samsung technology node, 13 metal layers are used.

acp sheet metal co inc

Each layer serves a specific purpose in the overall design, influencing the electrical conductivity, insulation, or other critical characteristics of the chip. Ion Implantation. Ion implantation is a critical technique in wafer fabrication, used to introduce dopants into semiconductor materials to alter their electrical properties and performance.metal layers on the chip and a matching footprint of solder bumps on wettable metal layers on the substrate. Flip-chip interconnection is an area array configurationin which the entire surface of the chip can be covered with bumps for the highest possible . The via is then filled with metal and overfilled, meaning that the metal deposition continues until a layer of metal is formed over the dielectric. The metal is then masked and etched in order to form metal lines,” Tokei said in .

action sheet metal los angeles

The electroplating process is a critical step in the fabrication of lab-on-a-chip devices, allowing for the precise deposition of conductive metal layers on various substrates. Understanding and optimizing the process parameters is paramount to achieving high-quality, functional microstructures within these devices.Besides, liquid metals serve as the sacrificial ink for fabricating 3D microfluidic chips. In terms of detailed procedures, it can be divided into three steps. The first step is to use a 3D printer to combine the liquid metal with the substrate. In this condition, the liquid metal oxide layer can further stabilize the microchannel shape.This concept can broadly be applied to future systems as it can be directly integrated into transceivers as graphene is compatible with CMOS processes.Fabrication process steps of proposed on-chip .

The die-area is a very valuable factor in chip-design, and should be reduced as much as the design allows it. Remember area = money. MIM Capacitor (Metal-Insulator-Metal) MIM capacitor is formed by two parallel metal layers and has a high k-dielectric between them. The button layer forms a small parasitic cap with the substrate. Copper is used to form the pillars that have bumps on top of them. 2 Under bump metallurgy (UBM): The metal layer formed under flip chip bumps. Redistribution Layer (RDL) Process Figure 4. An overview of the packaging process using a redistribution layer (RDL) Figure 5. The steps for forming a redistribution layer (RDL)Organic films are used in flip chip processing much the same way they are used in general wafer fabrication processing. Organic materials like polyimide or benzo-cyclobutene (BCB) are dielectric films with useful mechanical properties that make them suitable as stress buffer passivation layers that improve device reliability by eliminating stresses introduced during packaging operations.Second metal. The second metal layer is usually the thickest metal, often 4 microns thick but up to 6 microns is offered. . it is used in the fabrication of beam-lead devices such as certain diodes. In this case all of the material under the beam-leads is etched away. . Chips are picked from the wafer and placed in waffle packs or gel-packs .

Close-up images confirmed that microelectrode was not fractured, ensuring the ability to bond the metal electrode layer and the microchannel plate while maintaining the electrode intact. . Given that the current organ-on-a-chip fabrication methods mostly rely on PDMS, this bonding strategy will expand simple fabrication capability using . 1. Introduction. The establishment of lab-on-a-chip (LOC) technology made it possible to gradually integrate large and costly bench-top laboratory instruments into palm-sized devices containing chips in a scale of a few centimeters or less, without sacrificing their performance [].LOC-based devices have been used in molecular biology [], clinical diagnostics .

semiconductor wafer to chip

Thus, the layout of the LM microchannel is largely simplified. In addition, we used a two-layer lithography technique to fabricate the texture structure and the microchannel structure into the same layer. The double-layer lithography and chip fabrication process is .The amount of wires with only one additional layer can be reduced about 30 %. Between the wires, isolation layers are deposited, the metal layers are connected through vertical interconnect accesses (via). In today's microchips there are seven or more layers integrated.

semiconductor chip metallization material

To anyone who didn’t know, el pandillo distillery (g4, terralta, volans) uses this monstrous 19,000 lb tahona to crush their roasted agave—made from scrap metal parts from a nearby dump! .

how is metal layer used in chip fabrication|metal layers in semiconductor